Blog

jb® Super Capacitors – 5.5V & 7.5V Combined Type for IoT Backup

Overview

The jb Supercapacitor 5.5V portfolio leverages electrical double-layer capacitor (EDLC) physics for fast, low-ESR energy buffering in IoT edge nodes, smart meters, and industrial controls. Compared with batteries, EDLCs tolerate millions of shallow cycles, supply instantaneous pulse current, and recharge rapidly under intermittent power.

- Use cases: memory/RTC hold-up, brownout ride-through, wireless burst, actuator/motor pulse assist.

- Design focus: ESR & inductance minimization, thermal margining, stack balancing >5.5 V.

- Form factors: Coin (JGA), radial (JGW), low-ESR snap-in/screw (JGZ), combined 5–7.5 V (JGY/JGM).

EDLC Mechanism and Parameters That Matter

Energy storage arises from ion adsorption at high-surface-area carbon electrodes separated by a porous separator and electrolyte.

Key levers are pore-size distribution, ionic conductivity, and current-collector resistance, which jointly set ESR, frequency response, and lifetime.

See Simon & Gogotsi (Nature Mater. 2008) for materials-physics fundamentals and scaling behaviors.

- ESR vs. Ripple: ΔVripple ≈ Iripple·ESR; thermal P ≈ Irms2·ESR.

- Energy: E = ½·C·V2; Hold-up time (constant load): Δt ≈ C·ΔV / I.

- Leakage: dominates long idle periods; verify Ileak at temperature.

- Frequency: ESR and capacitance are frequency- and temperature-dependent; validate at operating conditions.

jb Supercapacitor 5.5V Series Overview

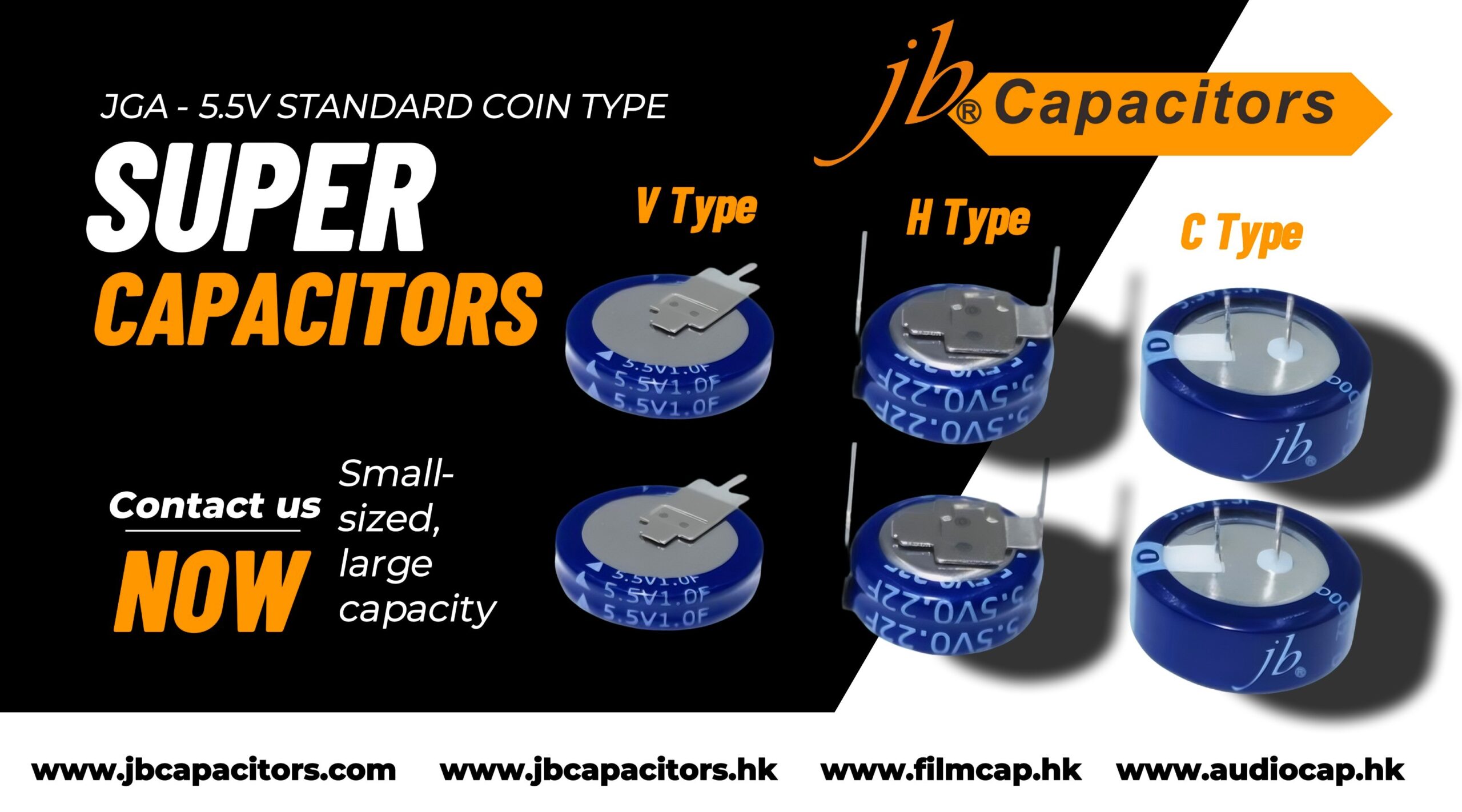

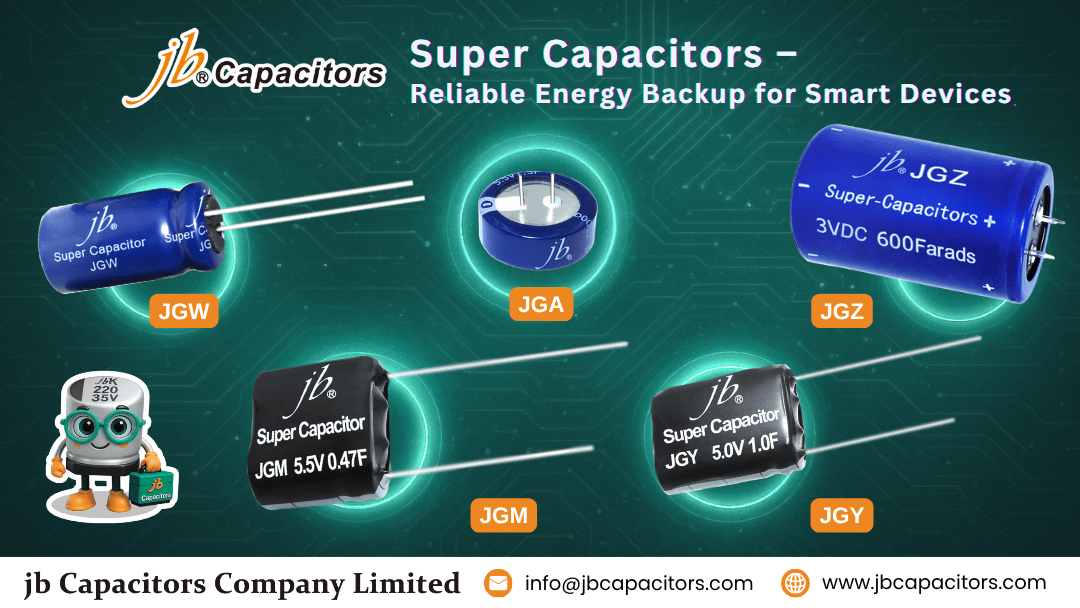

- JGA — Coin Type (5.5 V)

Compact RTC/memory backup for space-constrained boards; predictable ESR drift across life.

- JGW — Radial (≈3.8 V)

IoT nodes: balance of pulse capability and temperature robustness for outdoor meters.

- JGZ — Snap-in / Screw (2.7–3.0 V)

Ultra-low ESR for high pulse currents in motor drives, H-bridge hold-up, and energy recovery.

- JGY — Combined (5–7.5 V)

Low leakage, stable hold-up for telecom/embedded systems with higher bus voltages.

- JGM — Low-Resistance (5.5–7.5 V)

Optimized impedance for industrial/automotive high-current modules and compact power banks.

Right-Sizing a 5.5 V Supercapacitor (Worked Example)

Goal: Keep a smart meter MCU + RF module alive for Δt = 1.2 s at 3.3 V rail during a brownout. Load ≈ 220 mA burst, acceptable droop ΔV = 0.6 V (3.6→3.0 V via buck).

- Required C: C ≈ I·Δt / ΔV = (0.22·1.2)/0.6 ≈ 0.44 F.

- Ripple from ESR: to limit ΔVripple ≤ 50 mV at Iripple=0.22 A ⇒ ESR ≤ 0.05/0.22 ≈ 0.23 Ω.

- Thermal: P ≈ Irms2·ESR ≈ 0.222·0.23 ≈ 11 mW avg → ample thermal margin.

- Headroom: select ≥ 1.0 F, 5.5 V class to cover aging and low-temperature ESR rise.

Tip: For higher bus voltages, stack cells and implement balancing (below).

Integration & Reliability

- Series balancing: For stacks > 5.5 V, use passive bleed (e.g., 1–5 MΩ per cell; verify leakage budget) or active balancers for tighter tolerance.

- Layout: Keep supercap close to load/PMIC; minimize loop inductance with short, wide traces; add small ceramic bypass (e.g., 1–4.7 µF) for HF spikes.

- Inrush/charging: Limit charging current via series R, NTC, or controlled current source to meet USB/adapter limits and EMI.

- Temperature & life: Each +10 °C roughly halves life (Arrhenius heuristic). Derate vs. max ambient and self-heating (I2·ESR).

- Safety: Observe polarity; do not exceed rated V; consider PTC/thermal fuse for fault domains.

- Compliance: RoHS/Pb-free; check surge and withstand per target market (metering/industrial).

Design Checklist (Copy/Paste)

- ✅ Hold-up target (Δt) & allowable droop (ΔV) defined

- ✅ C sized with margin; ESR verified at min temp & target frequency

- ✅ Charging current limited; inrush and EMI analyzed

- ✅ Thermal (Irms2·ESR) & ambient derating budgeted

- ✅ Series/stack balancing and leakage budget validated

- ✅ PCB loop inductance minimized; local HF ceramic added

- ✅ Safety & compliance reviewed (rohs, surge)

Verified Open-Access Research References

- Simon, P.; Gogotsi, Y. (2008). Materials for Electrochemical Capacitors. Nature Materials, 7(11), 845–854. DOI: 10.1038/nmat2297

- Conway, B.E. (1999). Electrochemical Supercapacitors: Scientific Fundamentals and Technological Applications. Springer. DOI: 10.1007/978-1-4757-3058-6

- Wang, G.; Zhang, L.; Zhang, J. (2012). Review on Nanostructured Materials for Supercapacitors. J. Mater. Chem. 22, 23136–23151. DOI: 10.1039/C2JM32588A

- Lewandowski, A.; Galinski, M. (2021). Practical Design Considerations for High-Power EDLCs. Energies 14(2):342. DOI: 10.3390/en14020342

- Sciutto, A. et al. (2023). Charging dynamics via Poisson–Nernst–Planck modeling (preprint). arXiv. arXiv:2303.07859